题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

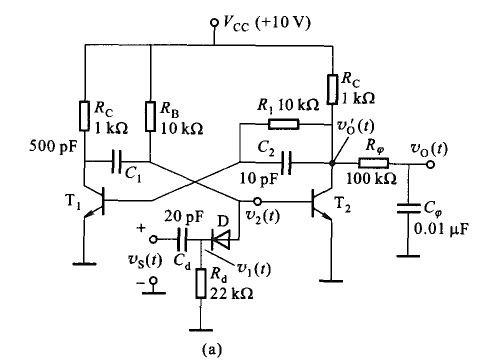

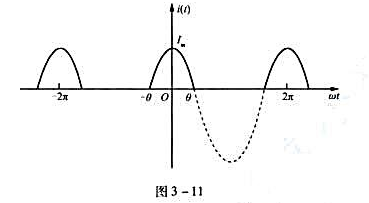

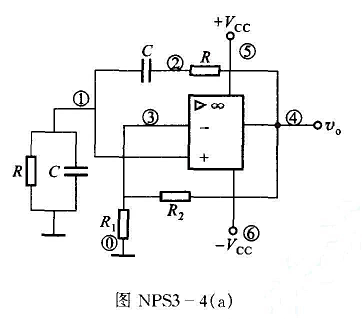

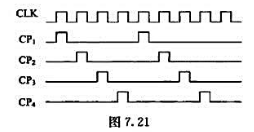

图NP5-16(a)所示脉冲计数式鉴频电路。图中,vs(t)是输入调频信号经限幅后的调频脉冲电压,,Cd⌘

图NP5-16(a)所示脉冲计数式鉴频电路。图中,vs(t)是输入调频信号经限幅后的调频脉冲电压, ,Cd和Rd构成微分网络将vs(t)变换为双向微分脉冲序列,而后利用晶体二极管D的单向导电性,将双向脉冲变换为单向脉冲,去触发由T1和T2构成的单稳态电路,产生调频方波,最后通过低通滤波器RφCφ。取出解调电压,试画出

,Cd和Rd构成微分网络将vs(t)变换为双向微分脉冲序列,而后利用晶体二极管D的单向导电性,将双向脉冲变换为单向脉冲,去触发由T1和T2构成的单稳态电路,产生调频方波,最后通过低通滤波器RφCφ。取出解调电压,试画出 的波形,并求出解调电压vo(t)的表达式。

的波形,并求出解调电压vo(t)的表达式。

提示:单稳态电路产生的调频方波,其峰值近似为[R1/(R1+Rc)]Vcc,宽度近似为0.69RBC1。

答案

答案

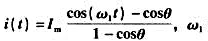

为i(t)的重复角频率]

为i(t)的重复角频率]

试分别求出VGS=2.5V、3V时的V0值,并进行分析.

试分别求出VGS=2.5V、3V时的V0值,并进行分析.